About Me

TL;DR: I just enjoy working with and exploring computer systems. I also have a deep interest in singing and playing the guitar.

Hello! I am a Senior at IIT Delhi, majoring in Electrical Engineering with a minor degree in Computer Science and Engineering. My academic journey gave me experiences starting from the transistor level details of memory systems to the high level abstraction of programming languages. Beyond my technical pursuits, I am also a music enthusiast, proficient in both singing and playing the guitar. I'm a dedicated admirer of art and literature, and I relish reading about technical advancements and global geopolitical events.

Feel free to connect with me to share insights, collaborate on exciting projects, or just chat about our shared interests and fields of expertise.

Looking forward to connecting and building meaningful professional relationships. Find my resume at:

Skills

Languages

Parallel Computing

Embedded and Cloud Computing

OS/Software

Projects

Linux Real Time Scheduler

This project was a part of the Operating Systems Course done under the guidance of Prof. Smruti Ranjan Sarangi. In this project I modify the Linux Kernel source-code to include a new Real Time Scheduling Class that implements the RMS algorithm.

I implement the necessary and sufficient schedulability tests, valid process state transitions using kernel data structures and system calls using which processes can register with the new scheduler. Here I use a Yocto Kernel for a minimal build configuration to accelarate the compilation and testing process. I was also awarded a place in the Hall of Fame for my project work in the course.

Neural Net with CUDA

This project was a part of the Parallel Programming Course done under the guidance of Prof. Rijurekha Sen. CUDA is NVIDIA’s parallel computing platform which allows us to create multithreaded programs that run on GPUs.

Artificial Neural Networks (ANN) involve computing convolutions layer by layer (weather it be feed forward or back propagation) and then eventually provide us with a output. After analusing we realise that the intra-layer computations could be done in parallel hence I used CUDA to parallelize these critical segments of an ANN in C++. Achieved up to 50% reduction in training latency, compared to naive sequential implementation, for complex models.

Google Page Rank

This project was a part of the Parallel Programming Course done under the guidance of Prof. Rijurekha Sen. Google presented a ground breaking computational model, MapReduce, back in 2004 that simplified data processing in a distributed system.

Here I use MapReduce to implement Google's own pagerank algorithm that it initially used for raking webpages on its search engine. Specifically, I first implement pagerank using an exiting C++ Map-Reduce library and then go ahead to implement my own MapReduce library in C++ using MPI (Message Passing Interface) from scratch that provides all the functions necessary for pagerank and then use this library to implement pagerank.

DS Coin

This project was a part of the Data Structures and Algorithms Course done under the guidance of Prof. Amitabha Bagchi and Prof. Venkata Koppula. Blockchain, in the simplest of words, is a data structure that securely stores information about the transactions that happens between the various participants in the network.

To capture all the functionalities of a blockchain we use an object oriented programing language (Java) for its implementation. We built an almost decentralised cryptocurrency using various data structures - Authenticated Linked Lists for a blockchain, Merkle Trees for transaction blocks and Queues for pending queues. We even modified the structure and the protocol to add transactions in the blockchain to make it more secure in order to safegaurd it from malicious miners.

Keyword Spotting on Cortex M4

Welcome to my B.Tech Project. This was done under the supervison of Prof. Rijurekha Sen and Prof. Saurabh Gandhi. Unlike Cortex-A processors which are used in our Laptops and PCs, Coretx-M processors are smaller, resource constrained, microcontroler processors with very small amount of RAM and Flash. These are used for very specific embedded applications and are able to run bare-metal code on them.

Our aim in this project was to implement Keyword Spotting (KWS) on a Cortex-M processor that will run on a wearable device and will trigger necessary functionality on speech command by spotting the relevant keyword. We employed system/processor performance optimizations & ML model compression for KWS on the processor and implemented input audio filtering to eliminate adversarial noise that even improves robustness for real-time keyword spotting.

Linux Context Switch Tracker

This project was a part of the Operating Systems Course done under the guidance of Prof. Smruti Ranjan Sarangi. In this project I modify the Linux Kernel source-code to to monitor the number of voluntary and involuntary context-switches of processes. I wrote some system calls to make use of the already defined process specific data structures (task-struct) in order to get the number of context switches experience by the process.

I also designed a Kernel Module to generate on demand signals for processes via the proc virtual file system. Defined some system calls using which processes can request the sugnal generator to send a signal to some other processes which is thereafter handeled by the module itself.

Simulating External Merge Sort

This project was a part of the Database Management Systems Course done under the guidance of Prof. Srikanta Bedathur. When we have large amount of data present in our hard-disk that needs to be sorted, all of it cannot be brought to the main memory at once because of smaller size of the main memory. In this situation we utilise the external mergesort algorithm to sort the datalot-by-lot.

In this project I simulate the exteral mergesort algorithm where a large amount of data (~1GB) is stored in a virtual hard-disk and we are using a virtual main memory (~5MB) to sort that data. I implement the algorithm in C++ and make use of the heap-sort algorithm to sort the in-memory data and dump it to the virtual disk until the entire data is sorted.

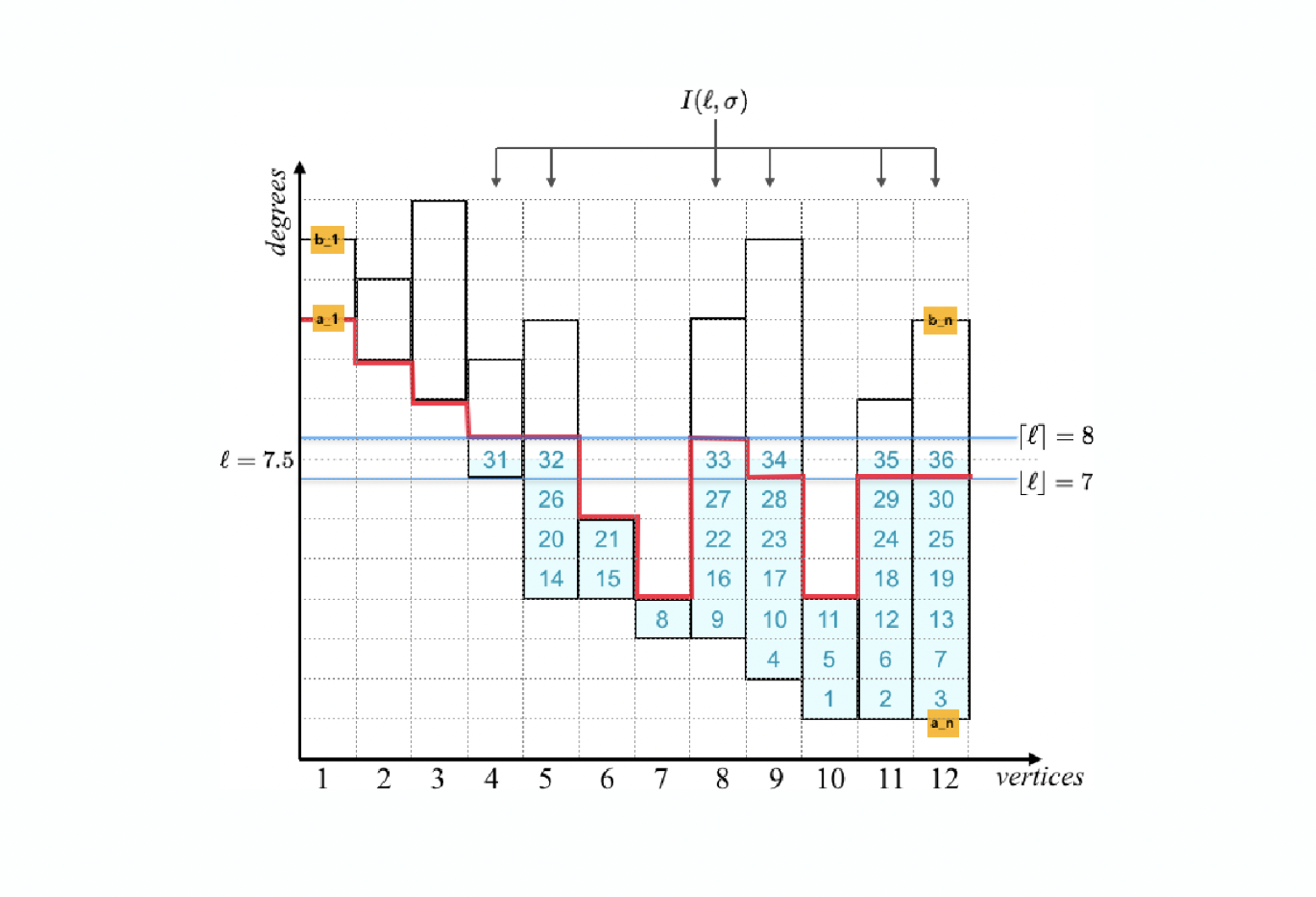

Interval Sequence Realizability

This was a research project done under the guidance of Prof. Keerti Choudhary and Prof. Venkata Koppula. The question being dealt here is, Given a sequence of intervals (/interval-pairs), does there exist an undirected (/directed) graph whose vertecies have degrees (/indegrees and outdegrees) within the corresponding intervals in the given sequence to "realise" the sequence?

This is termed as the interval sequence realizability problem. It has been well studied for undirected graphs but nothing is known for directed graphs. We worked towards giving a characterisation for an interval-pair seuquence that can be realised and provide a linear time algorithm to verify the realisability of the given interval pair sequnce.

We also took part in the SIAM Symposium on Simplicity in Algorithms in 2023 (SOSA23) with the research paper we wrote on this project.

Character Device Driver

This project was a part of the Operating Systems Course done under the guidance of Prof. Smruti Ranjan Sarangi. Here I design and implement a character device driver for a virtual LIFO device, whose size is practically unbounded. Two virtual LIFO devices are created that use the same device driver. One of the devices being read-only, while the other being write-only. The characters written to the write-only device can be read only from the read-only LIFO device.

I wrote a separate module for the driver that manages these two character devices. In the case when a reader is trying to read from an empty stack, it will enter a wait queue until signaled by some writter after it writes something to the stack. A simple driver can handle one reader and one writer easily, but to make the driver more resilient to concurrent accesses of multiple readers and multiple writers, I utilized kernel locks.